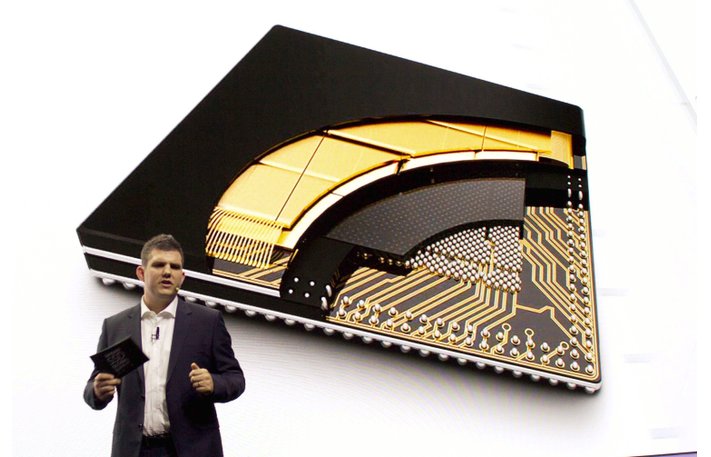

Intel Foveros 3D

Поскольку закон Мура больше не действует, разработчикам микросхем приходится искать иные способы повышения производительности. Одна из подходящих для этого технологий называется 3D-штабелирование (3D chip stacking). Это объёмная этажерочная архитектура чипов, в разработке которой лидирует Intel. Два месяца назад Intel представила архитектуру Foveros 3D: трёхмерную структуру, которая включает в себя CPU по техпроцессу 10 нм, чип ввода-вывода и сквозные вертикальные электрические соединения TSV (Through Silicon Via) в центре микросхемы, а сверху всей микросхемы — чип памяти.

На конференции по высокопроизводительным вычислениям Rice Oil and Gas HPC компания AMD заверила, что работает над собственным вариантом 3D-архитектуры чипов.

Старший вице-президент и генеральный менеджер Форрест Норрод (Forrest Norrod) рассказал, что компания разрабатывает несколько технологий, чтобы увеличить отдачу и обойти проблемы в связи с окончанием действия закона Мура и последствиями — прекращением роста плотности транзисторов и тактовой частоты.

Как и другие компании, AMD столкнулась с ограничением на площадь микросхемы около 700 мм² и вынуждена развивать 3D-архитектуру. Фирма уже применяет такой подход, размещая память HBM2 рядом с подложкой GPU, то есть она находится в том же пакете, что и процессор. Но в будущем компания планирует перейти к более продвинутому 3D-штабелированию.

Норрод сказал, что AMD работает над размещением памяти SRAM и DRAM непосредственно поверх вычислительных компонентов (например, процессоров и графических процессоров), чтобы обеспечить еще большую пропускную способность и производительность.

Samsung Polaris

Такой подход отличается от обычных реализаций package-on-package (PoP), которые просто помещают два готовых пакета друг на друга, как Норрод показал на примере чипа Samsung Polaris. В этом примере пакет DRAM соединяется через два дополнительных ряда разъемов BGA, которые окружают базовый чип. Эти разъемы BGA передают данные между двумя чипами. Как и в любом стандартном дизайне, логика находится в нижней части стека из-за необходимости в большем количестве разъёмов, но два кристалла не соединены напрямую. Таким образом, подход PoP обеспечивает максимальную плотность, но это не самый быстрый вариант.

В истинном 3D-штабелировании две матрицы (в данном случае памяти и процессора) расположены друг над другом и соединены вертикальными соединениями TSV, которые непосредственно сопрягают их. Эти соединения TSV передают данные между кристаллами с максимально возможной скоростью и обычно находятся в центре микросхемы, как мы видели на примере Intel Foveros 3D. Это прямое сопряжение повышает производительность и снижает энергопотребление (все перемещение данных требует питания, но прямые соединения оптимизируют процесс). 3D-штабелирование также позволяет увеличить плотность.

Норрод не углублялся в подробности разрабатываемых проектов, но это может оказаться фундаментальным сдвигом в дизайне процессора AMD.

Новая технология Intel Foveros 3D может оказаться определяющим моментом для отрасли, поэтому неудивительно услышать, что AMD движется в этом направлении, пишет издание Tom's Hardware.

Пока что нет никаких технических подробностей о технологии 3D-штабелирования от AMD, кроме того, что сказал на презентации Форрест Норрод (см. видеозапись ниже).

Комментариев нет:

Отправить комментарий