Борис Цирлин и Александр Кушнеров

30.10.2019

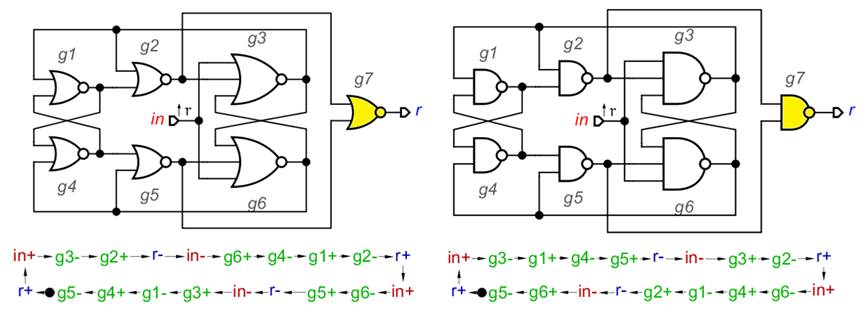

Для опытного разработчика схем не составляет большого труда узнать знакомую схему, в каком бы виде она не была нарисована. В этой статье мы покажем, что две транзисторные схемы из патентов являются вариантом асинхронного счётного триггера (АСТ). По сравнению со стандартной схемой, в схемах из патентов отсутствуют некоторые транзисторы. Это может рассматриваться как неисправность. Мы покажем, что, если такая же неисправность возникает в стандартной схеме, она продолжает работать правильно. АСТ, реализованный только на элементах ИЛИ-НЕ [1] или только на элементах И-НЕ известен как гарвардский триггер. Оба варианта схем показаны на Рис. 1, где g7 – это индикатор завершения переходных процессов. В дальнейшем мы его рассматривать не будем. На Рис. 1 показаны также графы сигнальных переходов (STG) [2] построенные в Workcraft [3].

Рис. 1. Асинхронный счётный триггер (АСТ) и его STG.

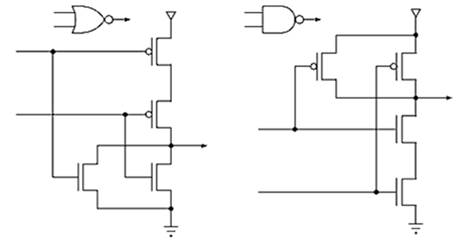

Обратим внимание, что в обоих вариантах АСТ есть три пары элементов (g1, g2), (g4, g5) и (g3, g6), которые имеют общий вход. Транзисторные схемы элементов 2И-НЕ и 2ИЛИ-НЕ показаны на Рис. 2. Трёхвходовые элементы устроены аналогично и содержат 6 транзисторов.

Рис. 2. Транзисторные схемы элементов 2И-НЕ и 2ИЛИ-НЕ.

Возьмём два элемента 2ИЛИ-НЕ и выберем у каждого вход, где p-MOS транзистор подключён к Uпит. Соединим эти входы вместе и подключим к земле (лог. 0). Оба транзистора откроются и напряжение на их стоках будет равным Uпит. Достаточно ли этого чтобы безопасно соединить стоки и заменить два транзистора на один, как показано на Рис. 3? Нет. Нужно проверить что произойдёт если на общий вход подать лог. 1. Выходы обоих элементов соединятся с землёй, и мы будем иметь мостиковую схему из четырёх p-MOS транзисторов. Для оставшихся двух входов имеем четыре комбинации 0 и 1. Легко показать, что ни в одной из них не возникает короткого замыкания между Uпит и землёй.

Рис. 3. Два элемента 2ИЛИ-НЕ, имеющие общий вход.

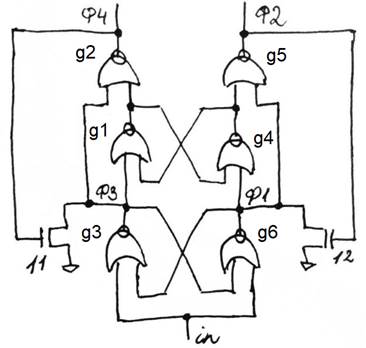

Рассмотрим теперь схему распределителя импульсов [4] на Рис. 4. Пользуясь Рис. 3, мы можем перерисовать эту схему как показано на Рис. 5. В ней уже можно узнать АСТ на Рис. 1, однако, там элементы g3 и g6 имеют 3 входа.

Рис. 4. Схема распределителя импульсов из [4].

Рис. 5. Вариант схемы на Рис. 4.

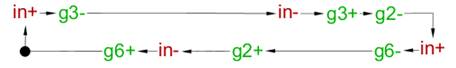

Затворы транзисторов 11 и 12 можно рассматривать как входы элементов 3ИЛИ-НЕ, в которых третий p-MOS транзистор закорочен. Влияет ли это на правильную работу схемы? Рассмотрим порядок появления сигналов in, g2 и g6 на входе элемента g3. Для этого удалим все остальные сигналы в соответствующем STG на Рис. 1 как показано на Рис. 6.

Рис. 6. STG для ИЛИ-НЕ. Сигналы in, g2, g6 и g3.

Поскольку третий p-MOS транзистор закорочен, переключение g3+ может произойти после переключений in- и g6- (в любом порядке) без разрешающего переключения g2-. Однако, как видно из Рис. 6, на участке от g2+ до g2- есть только in- и g6+, поэтому запрещённого переключения g3+ не происходит. Перед переключением g2+ элемент g3 уже находится в 0, а на его входе g6 всё ещё 0, т.е. первый p-MOS транзистор открыт. Переключение g2+ открывает транзистор 11 и должно выключить закороченный p-MOS транзистор. Этого не происходит, более того, переключение in- открывает второй p-MOS транзистор. Таким образом, через два открытых p-MOS транзистора и открытый транзистор 11 начинает течь ток от Uпит к земле. Это продолжается короткое время, пока следующее переключение g6+ не закроет первый p-MOS транзистор. В течении этого времени транзистор 11 обеспечивает 0 на выходе g3. Как именно? Допустим сопротивления открытых p-MOS и n-MOS транзисторов одинаковы и равны R, тогда после переключения in- напряжение на g3 подскакивает с 0 до (1/3)Uпит, но это в идеальном случае. На практике, между g3 и землёй есть какая-то паразитная ёмкость, напряжение на которой возрастает плавно и может не достигнуть (1/3)Uпит. Так или иначе, это напряжение будет меньше, чем (1/2)Uпит и означает лог. 0. Для транзистора 12 всё аналогично, он короткое время обеспечивает 0 на выходе g6. Таким образом, задержки элементов g6 и g3 определяют два отрезка времени, когда триггер потребляет большой ток примерно равный Uпит/(3R).

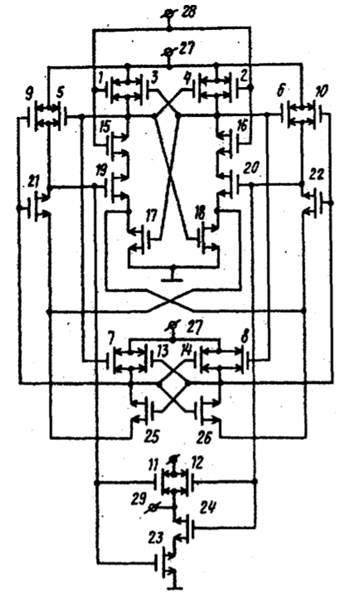

Рассмотрим теперь схему счётного триггера [5] на Рис. 7. Здесь транзисторы 11, 12, 24, 23 образуют элемент 2И-НЕ, который по видимому, является индикатором АСТ на Рис. 1. Другой элемент 2И-НЕ образован транзисторами 7, 13, 25 и 18. Обратим внимание на то, что транзистор 18 подключён к земле и аналогично примеру на Рис. 3, является общим для трёх элементов И-НЕ. Второй элемент 2И-НЕ, куда входит транзистор 18, образован транзисторами 5, 9, 21, а третий – это 3И-НЕ на транзисторах 2, 4, 16, 20. В параллель с транзисторами 2 и 4 должен стоять третий p-MOS транзистор, но он отсутствует. Схема на Рис. 7 симметрична, для лучшего понимания перерисуем её как показано на Рис. 8.

Рис. 7. Схема счётного триггера из [5].

Рис. 8. Вариант схемы на Рис. 7.

Будут ли выходы g3 и g6 на Рис. 8 переключаться правильно, если третий p-MOS транзистор в параллель отсутствует? Это будет понятно после анализа STG на Рис. 9, который, как и в предыдущем случае, получен из соответствующего STG на Рис. 1 удалением всех сигналов, кроме in, g2, g6 и g3.

Рис. 9. STG для И-НЕ. Сигналы in, g2, g6 и g3.

Элемент g3 – это 3И-НЕ, поэтому после переключений in+, g6+ и g2+ (в любом порядке) произойдёт переключение g3-. Любое из обратных переключений in-, g6- или g2- должно вызвать переключение g3+. Однако, g2- не может открыть отсутствующий p-MOS транзистор, поэтому g3 останется в 0 и будет ждать переключения in- или g6-. Как видно из Рис. 9, на участке от g3- до g3+ переключения g2- нет и p-MOS транзистор здесь не нужен. С другой стороны, этот транзистор должен обеспечивать лог. 1 на g3, когда in и g6 переключаются произвольно. Рассмотрим на Рис. 9 участок от g3+ до g2+. Переключение g2- закрывает транзистор 19. Далее, переключение in+ закрывает транзистор 1 и открывает транзистор 15. Элемент g6 остаётся в 1, т.е. транзистор 17 открыт, а транзистор 3 закрыт. Таким образом, in+ отключает g3 и от земли, и от Uпит. Тем не менее, на g3 удерживается лог. 1, поскольку на практике между g3 и землёй есть паразитная ёмкость, которая заряжена до Uпит. Переключение g6- открывает транзистор 3 и подключает эту ёмкость к Uпит. Для второй половины схемы всё аналогично. Таким образом, задержки элементов g6 и g3 определяют время, в течении которого состояние запоминается на ёмкости. На практике важно чтобы ток утечки транзисторов 19 и 20 был маленьким, иначе за отведённое время ёмкость может разрядится ниже (1/2)Uпит.

По сравнению со стандартным АСТ на Рис. 1, в схемах на Рис. 5 и на Рис. 8 функция установки в 1 элемента 3ИЛИ-НЕ и функция сброса в 0 элемента 3И-НЕ повреждена. Это означает, что стандартный АСТ продолжит работать правильно, даже если в элементах g6 и g3 возникнет соответствующая неисправность. Для стандартной схемы (без g7) нужно 28 транзисторов. Для схем на Рис. 4 и на Рис. 7 (без транзисторов 11, 12, 24, 23) нужно соответственно 23 и 22 транзистора. Если вернуть недостающие p-MOS транзисторы, эти схемы будут работать надёжнее. Минимальное количество транзисторов в схеме на Рис. 7 не обязательно говорит о том, что она лучше схемы на Рис. 4 и лучше схемы на Рис. 1. Помимо количества транзисторов и потребляемого тока есть другие важные параметры, например,

- сложность дополнительной схемы для установки начальных состояний

- нагрузочная способность (скорость перезарядки ёмкости нагрузки)

- скорость выхода из метастабильного состояния

- количество и значения паразитных ёмкостей

- количество и значения токов утечки

Сравнительный анализ этих параметров, как и обсуждение схем АСТ реализованных на других элементах, выходит за рамки этой статьи.

Литература

[1] G. T. Osborne, «Asynchronous binary counter register stage with flip-flop and gate utilizing plurality of interconnected NOR circuits». Patent US3139540, 30 Jun. 1964.

[2] Л. Я. Розенблюм и А. В. Яковлев, «О новой графической форме иллюстрации сущности изобретения,» Вопросы изобретательства, № 11, pp. 36-40, 1988.

[3] https://workcraft.org

[4] В. И. Горячев, Б. М. Мансуров, Я. Д. Мартыненко и Р. Г. Талибов, «Четырехфазовый распределитель импульсов». Авторское свидетельство SU342299, 14.06.1972.

[5] В. И. Варшавский, Н. М. Кравченко, В. Б. Мараховский и Б. С. Цирлин, «Счетный триггер на КМОП-транзисторах». Авторское свидетельство SU1398069, 23.05.1988.

Комментариев нет:

Отправить комментарий