Большая часть печатных плат, трассировкой которых я занимался, малогабаритные, с высокой плотностью монтажа и применением бескорпусных микросхем – специфика разработки СВК (англ. SIP), а в остальных случаях тоже удавалось обходиться электрически короткими линиями. На одной из последних плат потребовалось использовать ассиметричные линии управления длиной порядка 15 см, причём в спецификации на одну из микросхем фронты сигнала tR были заявлены равными 2 нс. Напомню (статья здесь, чтобы много не повторяться), что критерием электрически короткой линии является:

где TD – временная задержка линии. Я часто встречал ½ в этой формуле, но указанный критерий более жёсткий, поэтому использовать лучше его, а для остальных случае применять моделирование.

Очевидно, что критерий не выполняется. Стал читать про согласование и понял, что этот раздел в книге мне не очень нравится. Как раз потому, что на практике я серьёзно с этой задачей не сталкивался. Стал разбираться и нашёл неплохую статью про согласование, где, в частности, есть рекомендации по согласованию для различных типов сигналов. Для КМОП-сигналов рекомендовалась последовательная схема, что, собственно, логично.

В качестве управляющей микросхемы в проекте используется ПЛИС, поэтому решил промоделировать распространение сигнала в линии. Для этой задачи используются IBIS-модели, содержащие стандартизованное описание параметров входных и выходных каскадов микросхем. Вот неплохая краткая статья, дающая базовое представление о структуре IBIS-моделей.

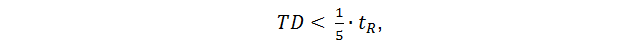

Скачал IBIS-модель ПЛИС с сайта производителя, теперь нужно было её прикрутить к линии передач и выполнить моделирование. Самым простым и доступным решением, что я нашёл – это использование «старого-доброго» Micro-Cap, который теперь ещё и абсолютно бесплатный. Вот здесь читаю описание того, как применять IBIS-модели. Не работает. Ладно, нахожу ту же самую IBIS-модель, на которую ссылается руководство, скачиваю, повторяю схему (рис. 1) уже один-в-один. Всё равно не работает.

Я уже думал пробовать в Altium Designer моделирование выполнить, но обращаю внимание на строчку в текстовом описании параметров компонентов (рис. 2) – активный уровень у разрешающего сигнала низкий. Меняю схему, всё работает, сначала 74AHC00, а потом и нужная мне IBIS-модель ПЛИС. Дальше уже дело техники – по использованию Micro-Cap есть видео-уроки.

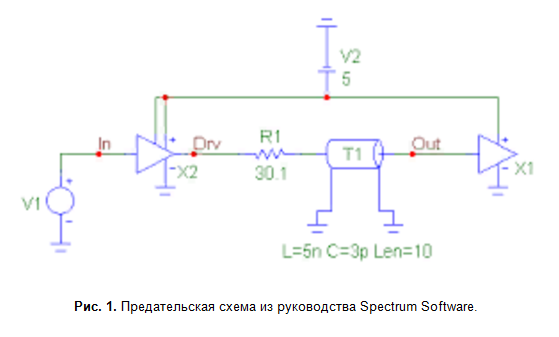

Добавить IBIS-модель в схему достаточно просто при всём неудобстве Micro-Cap в целом. Меню Component → Analog Primitives → IBIS → IBIS_Output5 или IBIS_Input3. В появившемся меню IBIS Model Creator (рис. 3) указываем путь к файлу модели *.ibs и выбираем конкретную реализацию. Здесь же графически отображаются параметры модели – типовые и предельные.

С помощью схем, представленных на рис. 4, определяются выходные сопротивления драйвера для высокого и низкого уровней напряжения. Это нужно для выбора согласующего резистора RSER = Z0 — ROUT, здесь ROUT — среднее значение между ROH и ROL.

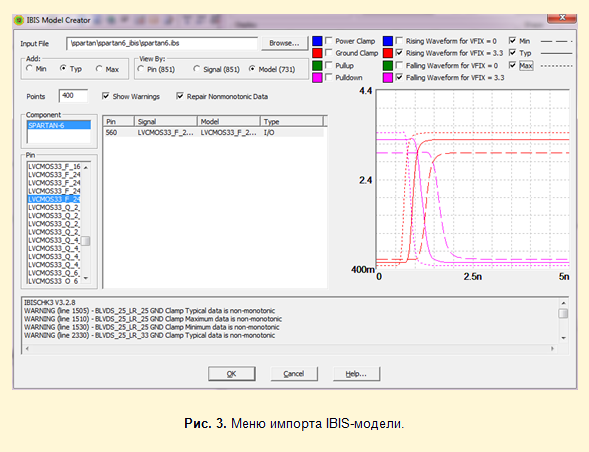

Для ПЛИС выходные каскады конфигурируемые, поэтому в IBIS-модели огромное количество вариантов, которые отличаются типом выхода, уровнями напряжения, нагрузочной способностью, скоростью нарастания фронта. Мне нужны были 3,3-вольтовые КМОП, у Xilinx их три типа, в зависимости от длительности фронта – Fast, Slow и QueitIO. Перебирая различные варианты драйвера в упрощённой схеме сигнальной линии (рис. 5), пришёл к выводу, что на стороне ПЛИС обойдусь конфигурированием и в дополнительных согласующих резисторах нет необходимости.

P.S. Раздел по согласованию в своём руководстве доработаю в следующем релизе, как время появится. Процесс познания бесконечен. Кстати, нашёл импортного коллегу с аналогичным руководством. Он молодец и здорово развернул проект, но книга не вдохновила. Так что считаю, что задача импортозамещения в данном конкретном случае проходит успешно :).

Комментариев нет:

Отправить комментарий